Einleitung

Ziel unserer Teilgruppe war es einen Timer zu entwerfen, der beim High Signal hochzählt, eine Spannung für ein Intervall hält und gleichzeitig den Schalter zwischen Sensorik und Auswertegruppe öffnet und somit die Übertragung für genau dieses Intervall unterbricht.

Aufbau

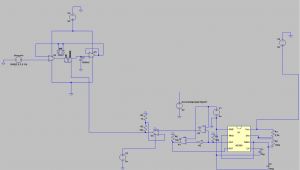

In den ersten Terminen wurde überlegt welche Aufgaben die Gruppe erledigen muss und wie diese aufgeteilt werden. Hierbei wurden Blockschaltbilder zur Visualisierung genutzt. DanachwurdedieRealisationderAufgabenüberlegtundüberverschiedeneLösungswege, mittels Internetrecherche, informiert. Hierbei hat man sich schnell auf den NE55 als Taktgeber geeinigt und sich gegen eine variable Periodendauer entschieden, welche mit Potentiometern oder einer zählenden Flip-Flop-Schaltung realisierbar wäre. Die Teilschaltung besteht entsprechend aus einem NE555 der als Zähler dient für die Dauer, die die Signale der Sensorik-Teilgruppe gehalten werden. Da die Sensorikgruppe nicht permanent Signale an die Auswertegruppe gibt, die durchgehend mit der Auswertung ständig neuer Signale beschäftigt wäre und das einen zu hohen Stromverbrauch zur Folge hätte, überlegten wir uns den NE555 der astabilen Kippstufe mit 2 Widerständen und einem Kondensator so schalten, dass er eine Periodendauer von 15 Sekunden aufweist. Nach Absprache mit den anderen Teilgruppe wäre dies der ideale Zeitabstand. Da der NE555 nicht durchgängig zählen soll, muss dieser gestartet und gestoppt werden, was mittels eines Signal von der Auswertungsgruppe geschieht. Dieses Signal ist entweder ein „Low“(0V),wenndieAusrichtungderSolarzellenichtstimmtundderSchaltersomitnicht betätigt oder ein „High“(5V), wenn die Ausrichtung stimmt und der Schalter betätigt werden soll, was zur Folge hat, dass es keine weiteren Signale von der Sensorikgruppe mehr gibt, die ausgewertet werden müssten, bis der Schalter nach Ablauf der gewählten Periodendauer wieder schließt. Sobald das Signal auf „High“ ëingeht, wird über eine Logikschaltung der NE555 gestartet und die NMos, welche die Sample-and-Hold-Schaltung steuern,, leiten. Die Sample-and Hold-Schaltungen unterbrechen und speichern die SIgnale für die Richtungen „links, rechts, oben, unten“ zwischen der Sensorik und der Auswertungsteilgruppe. Sie bestehen aus den beschriebenen NMos, welche als Schalter fungieren, je einem Kondensator pro Signal mit dem das Signal, das beim Öffnen des Schalters von der Sensorikteilgruppe kommt, gespeichert wird und je 2 OPVs, welche dafür sorgen, dass der Kondensator sich nicht entlädt während das Signal gehalten wird.

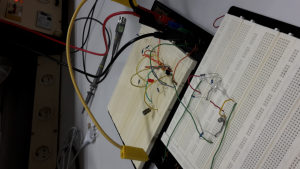

Zu Beginn haben wir uns den NE555 in der astabilen Kippstufe angesehen, einen Vortrag darüber gehört und das anschließend auf der Steckplatine nachgebaut. Um das Auf- und Entladen des Kondensators zu simulieren haben wir an Pin 3 des NE555, der den Output dessen wiedergibt, eine Diode mit in Reihe geschaltetem Widerstand nachgebaut und uns somit das Aufladen des Kondensators angezeigt. Lädt sich der Kondensator über die beiden Widerstände auf, erhalten wir an Pin 3 ein High Signal, was unsere Diode zum Leuchten brachte. Abschließend haben wir die Periodendauer, also die Zeit in der sich der Kondensator Auf-und Entlädt auf dem Oszilloskop nachgemessen. Die dafür verwendeten Kenngrößen sind: R1 =2.2kΩ,R2 =100kΩ,C =10−5F.

Aufbau mit NE555 als Taktgeber und Transistor als Schalter

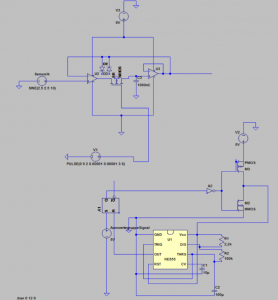

Als wir soweit waren, mussten wir uns darum kümmern, dass der NE555 aufhört zu zählen.InderbishererklärtenAnordnungzähltderNE55515Sekunden,derKondensator läd sich auf und entlädt sich mit jeweils ca. 7.5 Sekunden wieder und startet dann von vorne. Da das allerdings auch einen Stromverbrauch zur Folge hat obwohl das, solange kein High von der Auswertungsgruppe kommt, nichts bewirkt, haben wir uns überlegt, ein S-R-Flip-Flop einzusetzen, wie in Abb. 19 2. Nachgebaut funktionierte das allerdings nicht, da die Spannung, die dann am NE55 an Pin 8 ankam zu gering war um diesen zu starten. Dieses Problem führte zu der Implementierung über AND-Gatter.

Aufbau mit S-R-FlipFlop und Schalter

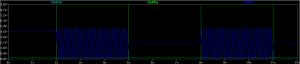

Nachdem wir einige Versuche starteten und z.B. Bei der Sample-and-Hold-Schaltung zwei gegensätzlich gerichtete Dioden einbauten, funktionierte die von uns überlegte Logik. Die Signale, die die Sensorikgruppe weitergibt haben wir mit einem Sinussignal simuliert, sodass wir in LTSpice testen konnten, ob das Signal gehalten wird. Abbildung 3 zeigt, dass uns das mittels Sample-and-Hold-Glied gelungen ist.  LT-Spice Simulation des Sample-and-hold-Glieds.

LT-Spice Simulation des Sample-and-hold-Glieds.

Die nächste Abbildung zeigt die fertige LTSpice simulation, wie sie in Eagle nachgebaut wurde.

Nach der Absprache mit der Auswertegruppe, mit der wir uns eine Platine teilen um weniger Busanschlüsse zu gebrauchen, wurde die Platine zum Drucken abgegeben und die vorgesehenen Bauteile gelötet. Das endgültige Platinenlayout kann man der Auswertegruppe entnehmen, da beide Teilgruppen auf eine Platine positioniert wurden, um zusätzliche Buseingänge zu sparen.