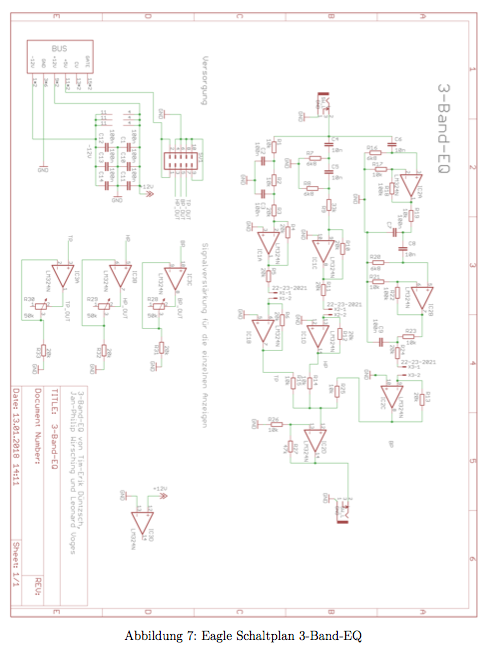

Nach der LTspice Zeichnung und erfolgreicher Simulation der Schaltung, wird mit Eagle das Platinenlayout erstellt. Dabei müssen bereits die Spezifikationen der realen Bauteile berücksichtigt werden. Hier werden als regelbare Widerstände logarithmische Schiebe- potentiometer eingesetzt und mit Molex-Steckverbindern an die Platine angeschlossen. Die drei Anzeigen für den Equalizer werden mit einer Busleitung an die EQ-Platine an- geschlossen. Die drei Signale werden nach den Filterschaltungen direkt abgegriffen. Vor dem Display-Bus-Output werden die Pegel auf jeweils ± 5V peak to peak verstärkt. Hier wird jeweils eine Verstärkerschaltung mit Potentiometer verbaut, sodass man später die gewünschten Pegel exakt justieren kann. Da jeder IC Abblockkondensatoren benötigt, haben wir jeweils in der Nähe einen 100 nF Kondensator eingebaut. Damit wird die Ver- sorgungsspannung gefiltert und es kann ein konstantes Spannungsniveau, trotz kurzer Spitzenströme, gewährleistet werden.

Die Belegung der 16 Pole des Busses wurde festgelegt. Der 1. und 2. Pin wird mit -12V und der 9. und 10. Pin wird mit +12 V belegt. Mit diesen Spannungen werden die IC’s versorgt. Die +5V wird durch den 11. und 12. Pin belegt. Diese Versorgung wird mit dem 10-Pol-Bus für die Verbindung der Anzeige weitergeleitet. Dafür wird der 1. und 2. Pin des 10 Pols angesetzt. Die restlichen Pins des Haupt-Busses sind mit der Masse verbunden.

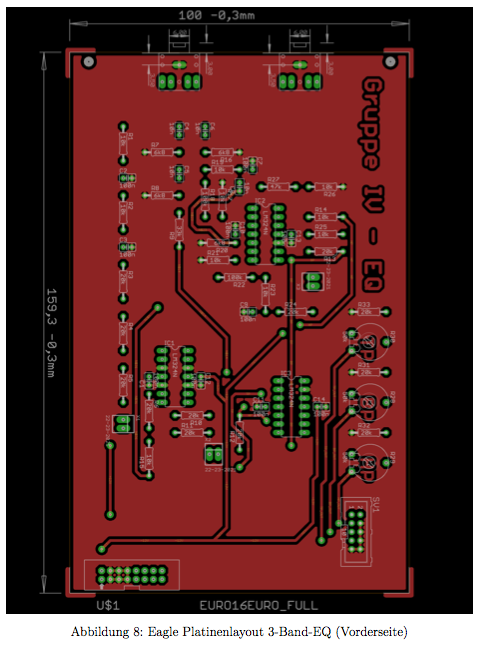

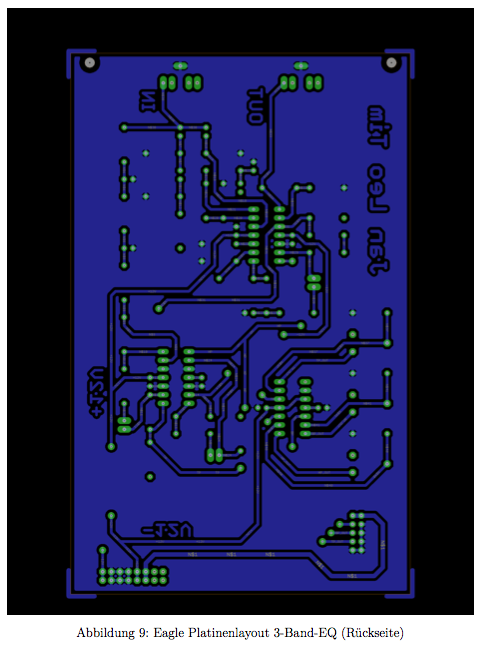

Die Ausgangssignale der Bänder wurden am 3., 5. und 7. Pin des 10 Pols festgelegt. Am 3. Pin liegt das Ausgangssignal des Hochpasses. Beim 5. Pin befindet sich das Aus- gangssignale des Bandpasses und beim 7. Pin liegt das Ausgangssignal des Tiefpasses. Die restlichen Pins sind wieder mit der Masse verbunden. Die Größe der Platine erfolgt anhand der Maße einer Europakarte. Der Maß der Platine beträgt 100 mm x 159.3 mm. Zuallererst haben wir versucht das Design auf einer Seite zu entwerfen. Da die Maße der Bohrungen jedoch zu gering eingeschätzt wurden, verwarfen wir diese Idee. Außerdem waren die Leiterbahnen zu nah aneinander. Daraufhin erfolgte das Design auf 2 Seiten.

Das Endergebnis für die Vorder- und Rückseite der Platine befindet sich im Anhang in der Abbildung 8 und 9.

(Leonard Voges, Tim-Erik Düntzsch, Jan-Philip Wirsching)

78

79

80

(Leonard Voges, Tim)