Die Gruppe ADSR setzt sich mit der Entwicklung eines Trägersignals auseinander. Dieses Signal besitzt Informationen über die Länge und Ampltitude des Tastenanschlages.

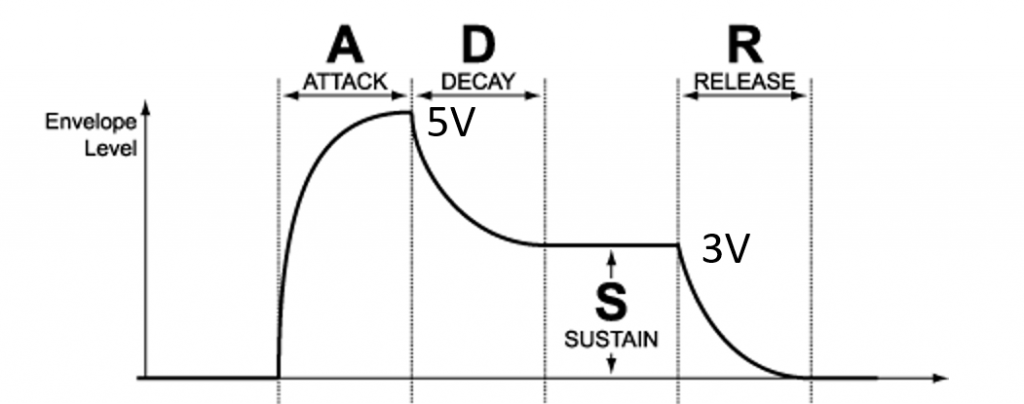

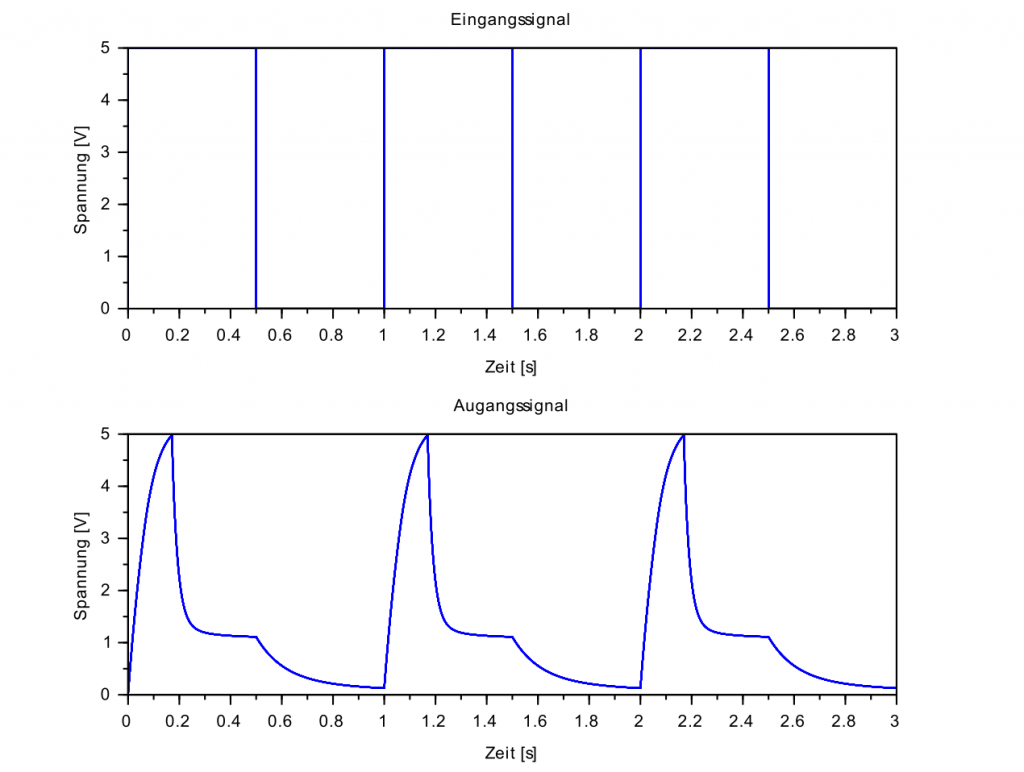

Die hier angesprochene Hüllkurve kann in folgender Abbildung eingesehen werden:

Abbildung: Ausgangsspannung der ADSR, „Hüllkurve“

In Attack wird ein Elko aufgeladen, in Decay wird er entladen, in Sustain wird die Spannung über dem Elko gehalten und in Release wird sie losgelassen.

Durch Veränderung der Werte an den Potentiometern, können die Längen der einzelnen Bereiche verändert werden.

Sustain kommt eine besondere Stellung zu, dieses Potentiometer regelt einen Spannungsteiler, welcher die Funktion hat, das Sustainniveau in seiner Höhe zu verändern.

Suche nach einem Schaltplan

In der Recherche gab es eine Auswahl von zwei Schaltungen.

Die erste ADSR Schaltung von „yusynth.net“ war zu komplex. Sie deckt einen Frequenzbereich von 0.1 bis 1000hz ab, sodass Tonsignale von 1ms bis 10s erzeugt werden konnten.

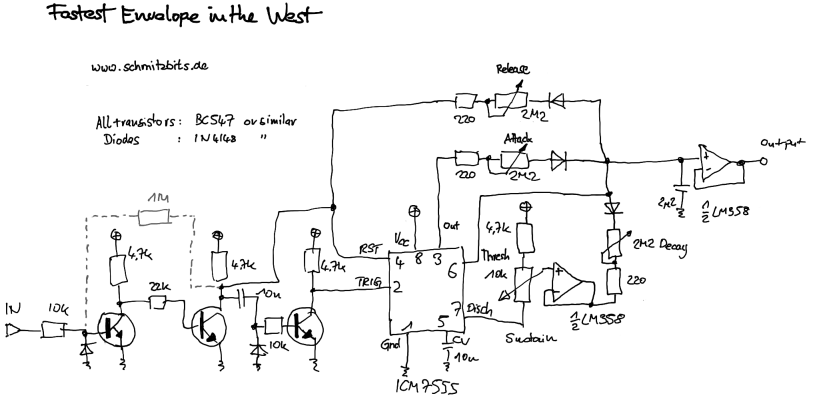

Benötigt wurde jedoch nach eigenem Ermessen nur ein Tonsignal von 0.5s bis 5s Länge. Eine Invertierungsfunktion wurde ebenfalls nicht benötigt, sodass sich die ADSR einfacher implementieren lässt, wenn man sich die ADSR Schaltung von ’schmitzbits.de‘ anschaut. Sie trägt den Namen ‚Fastest Envelope in the West‘ und zeichnet sich dadurch aus, dass der Ast, den sich Sustain und Decay teilen, separat durch Potentiometer gesteuert werden kann. Dies erfolgt durch einen Spannungsfolger, den man zwischen Sustain und Decay setzt. Eine solche Konfiguration lässt die Steuerung der Decay Fallzeit und des Sustain-Niveau unabhängig voneinander zu.

Dies wird in folgendem Schaltplan deutlich:

Abbildung: ADSR-Schaltplan von Schmitsbits.de

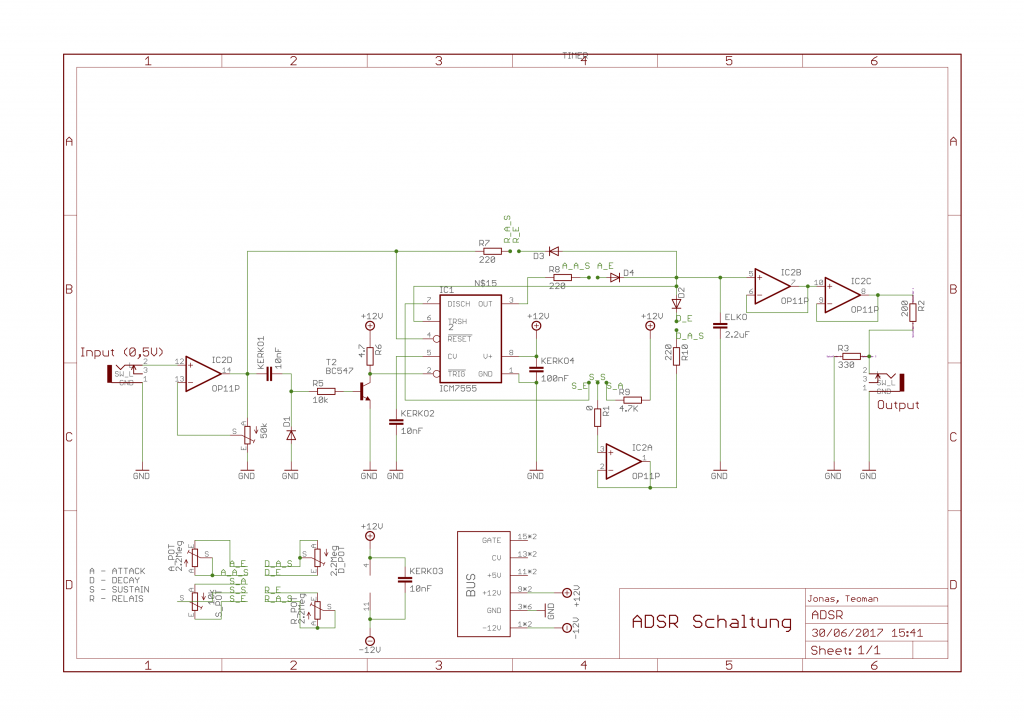

Im Anschluss konnte die Schaltung noch vereinfacht werden. Man siehe sich dazu auf der folgenden Seite den ersten Block links an. Der Teil wurde in einen nicht invertierenden Verstärker umgebaut, der auch als Folger arbeitet, sofern sich der komplette Potentiometer Widerstand im GND-Kanal befindet.

Weit rechts im Schaltplan fällt auf, dass zwei Folger und ein Spannungsteiler hintereinander geschaltet wurden, worauf später genauer eingegangen wird.

Abbildung: ADSR-Schaltplan verbessert

Funktionsweise

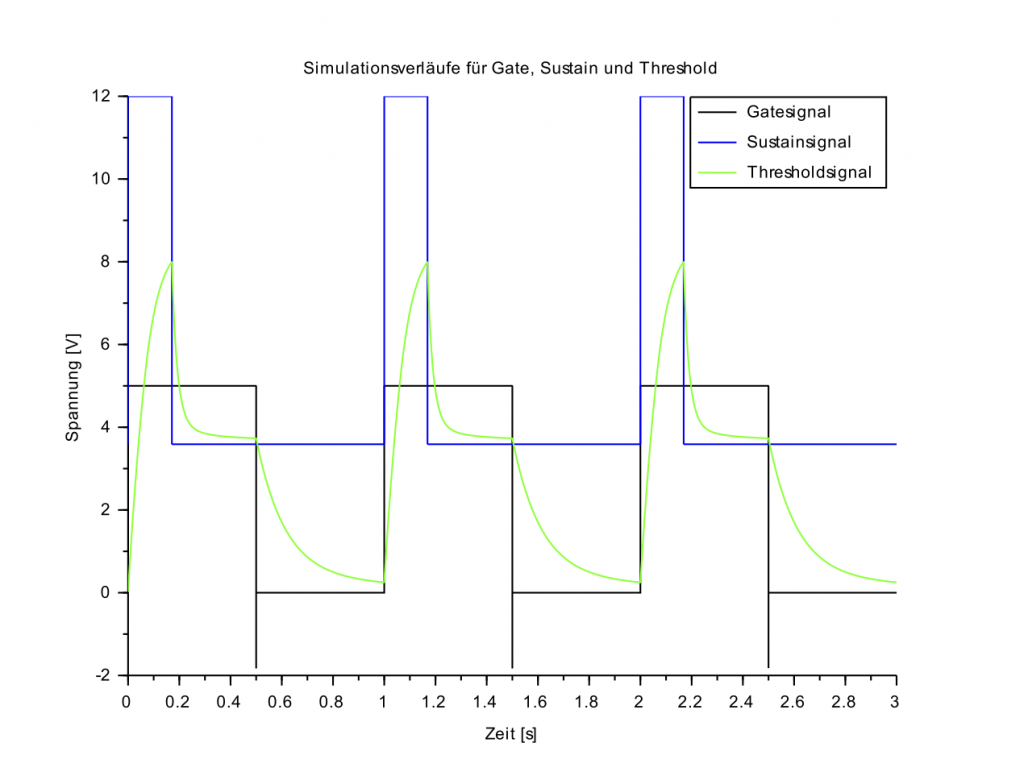

Abbildung: Wichtige Signalverläufe

Um die ADSR zu verstehen, sollte man Kenntnisse über die Funktionsweise eines Timer-Bausteins besitzen. Im Rahmen des Praktikums wurde die Funktion in einem der Vorträge detailreich beschrieben. Bei der folgenden Beschreibung wird davon ausgegangen, dass der Leser die innere Verschaltung eines Timers kennt und seine Funktion nachvollziehen kann.

Es lässt sich für den vorgeschalteten Block, links von Trigger Eingang des ICM7555 Timers, sagen, dass dieser die Funktion eines Low Aktiv Pulsers erfült. Immer wenn das Gate Signal eine steigende Flanke besitzt, so gibt der Pulsgeber ein GND Signal an den Trigger Eingang.

Der ICM7555 Timer hat drei Signale an seinen Eingängen anliegen, anhand derer die Funktion der ADSR vollständig beschrieben werden kann.

Das erste Signal nennt sich Gate und liegt am Reseteingang des Timers an. Das Gate Signal wird vom Interface geliefert und beinhaltet Informationen über die Länge des Tastenanschlages.

Das zweite Signal nennt sich Threshhold und liegt am entsprechenden Eingang des Timers an. Dieses Signal ist immer genauso groß wie die Spannung des Elkos.

Das dritte Signal nennt sich Sustain. Es beinhaltet die 12V Amplitude, welche sich in der Attackphase ergibt. Attack ist der Zustand, indem der Elko mit konstanter Timer Ausgangsspannung (Out) aufgeladen wird. Das namensgebende Sustain-Niveau von hier ungefähr 4V wird durch einen Spannungsteiler realisiert, dessen Abgriff in den in den Spannungsfolger geht, welcher in der Einleitung erwähnt worden war.

Angenommen die ADSR bekommt ein Gatesignal geliefert. Infolgedessen produziert der Low-Aktiv-Pulser als Antwort auf eine steigende Flanke ein GND Impuls der den Triggereingang des Timers auf GND legt. Im inneren des Timers vergleicht Komparator 2 das GND Signal mit 1/3 V_cc = 4V und setzt aufgrund dessen den Zustand im Flipflop auf 1, dies ist gleichbedeutend mit einem Ausgang auf logisch 1, sodass es erst einmal zu einem Ausgangssignal (Out) von 12V kommt, was sich als 12V Peak in der Abbildung wiederfindet. Nun beobachtet man aber, dass das Ausgangssignal irrgendwann nicht mehr vorhanden ist. Dies hat seine Ursache in einer ansteigenden Thresholdspannung (Elko-Spannung).

Übersteigt die am Threshold Eingang anliegende Spannung vom Elko, die Spannung im inneren des Timers 2/3 V_cc = 8V, so wird der Flipflop auf 0 gesetzt und der Ausgang ebenfalls. Gleichzeitig öffnet sich eine Leitung nach GND, die sich am Discharge-Eingang des Timers bemerkbar macht. Schaut man wieder in die Abbildung, so sieht man das das Threshholdsignal zu keiner Zeit über 8V hinauswächst. Beim Schalten des Timers kann nun über den geöffneten GND Kanal der Kondensator über Discharge entladen werden. Dies geht jedoch nur solange, wie die Spannung des Kondensators größer ist als jene Spannung des Sustainniveaus, welches sich durch den o.g. Spannungsteiler ergibt.

Der Spannungsfolger im Sustainzweig (S) lässt nämlich an der Diode D2 die Sustainspannung wirken, die der Spannung vom Kondensator entgegenwirkt. Sind beide Spannungen gleichgroß, so fließt kein Strom durch die Diode, was zur Folge hat, dass der Kondensator sich nicht weiter entladen kann. Nun kann man sich jedoch fragen, warum der Strom nicht durch D3 im Release Zweig abfließt. Ursächlich dafür ist das anliegende Gate-Signal von 5V, welches die Elko Spannung von 4V übertrifft. Über Diode fällt somit ein 1V Differenz in Sperrrichtung ab, sodass kein Strom durch sie fließen kann.

Als nächstes fällt in der Abbildung auf, dass das Threshold Kondensator Signal abfällt, sobald das Gate-Signal sein Ende erreicht. Dies hat seine Ursache darin, dass beim fehlen eines Gate-Signals die Elko Spannung größer ist, als die Spannung im Release Zweig, sodass ohne Probleme ein Strom durch D3 nach GND fließen kann.

Dimensionierung der Schaltung

Die Dimensionierung der ADSR Potentiometer kann durch Abschätzung mittels Zeitkonstante erfolgen. Der Kondensator wird über ein RC Glied aufgeladen, wobei jene Konstante beschreibt, wie viel Zeit vergehen muss, um 60% des Spanungsendwertes zu erreichen: τ = RC = 2.2 MΩ * 2.2uF ≈ 5s

Durch plotten der Funktion fällt auf, dass das Signal sich damit in einem Bereich von 5 bis 20 Sekunden befindet. Dies ist ein Problem für Gate-Signale, die kürzer sind, da die Attackphase alle anderen Phasen überdecken würde, sollte es sich um ein 0.5s Gate Signal handeln.

Ein 220nF Kondensator macht die Attackphase auch für Signale über 0.3 Sekunden nutzbar.

τ = RC = 2.2 ≈ 0.05s

Es sei darauf hingewiesen, dass sich die Schaltung weder in Simulation noch in der Praxis präzise nach diesen Vorschriften verhält. Es wird vermutet, dass neben den Potentiometer Widerständen noch weitere Widerstände der linksseitigen Schaltung involviert sind und den Zusammenhang komplizierter machen. Decay lässt sich im Grunde genauso abschätzen, doch wird dieses Niveau von Sustain überlagert, sodass der Zeitkonstanten Ansatz auch nur bedingt etwas über die wirkliche Fallzeit aussagt.

Bei einer fallenden Exponentialfunktion wird nach einer Zeit τ 40% des Ausgangswertes erreicht. Bei 8V Maximalwert sind das 3.2V. Um für Decay ein ähnliches Verhalten, wie für Attack zu erhalten, wird ebenfalls 2.2 MΩ verwendet.

Das Sustain Niveau kann durch einen Potentiometer Spannungsteiler eingestellt werden. Durch Verwendung von 10kΩ kann ein Teilerverhältnis von 1 / 13.7 realisiert werden. Diese schiefe Zahl ergbit sich aus dem Vorwiderstand plus dem Potentiometerendwert. Sollte Sustain die Elko Spannung auf 5V halten, so kürzt dieses Niveau die Fallzeit von Decay, da Decay seine 3.2V nach Zeitkonstante nicht erreichen kann.

Der Release Zweig verhält sich analog zu Attack und Decay.

Die zwei hintereinander gechalteten Spannungsfolger waren im Nachhinein die einzige realisierbare Lösung um der Schnittstellen Anforderung von 5V zu genügen. Im besten Fall sollte man den Spannungsteiler kurz vor dem Output zwischen die beiden Folger bringen, sodass eine Ausgangsseitige Schaltung nicht unabsichtlich über einen winzigen Widerstand auf GND gezogen wird (kann auch mit einer Diode verhindert werden, Spannungsabfall beachten). Der Ausgangsseitige Spannungsteiler wurde so konzipiert, dass er ein Teilerverhältnis von 5/8 besitzt. Damit werden 8V am Elko auf 5V am Ausgang reduziert.

Simulation

Die Simulation des oben angefügten Schaltplans mittels LT-Spice erbrachte folgende Hüllkurve:

Abbildung: Simulation des ADSR Ausgangssignals

Prototypenbau

Im Protypenbau hätte eine strukturierte Fehlersuche Zeit ersparen können. Zum Beispiel musste oft der richtige Pin aus Datenblättern ausgelesen werden, um ihn zu testen. Außerdem wurde oft rückwärts getestet, d.h. vom Output hin zur Quelle, weil angenommen wurde, dass die Änderung am Output eine Änderung der Schaltung zur Folge habe. Doch meistens waren die Inputs nicht mehr richtig!

Daher bietet sich in Zukunft folgende Checkliste an. Überprüfe nacheinander:

- Outputknopf der Quellen

- Amplitudenhöhe der Quellen

- stromtragende Inputs

- Steckverbindungen der Bauteile

- Outputs von Timer, Elko, OPV

Nach dem Aufbauen der Schaltung auf dem Steckrett fiel auf, dass der Ausgang mit 0.3V viel zu klein ist. Dieser Fehler konnte nicht behoben werden, und lag vermutlich an einem defekten Steckbrett. Mit der Annahme, dass die fertige Platine auch niedrige Spannungen Ausgeben wird, wurde ein Ausgangsverstärker eingeplant.

Eagle Schaltungsentwurf

Die Schaltung wurde in Eagle implementiert und ein Platinendesign daraus erstellt.

Es kann festgehalten werden, dass der Routing Prozess iterativ von Gange geht, sodass erst mehrere Anläufe zu einem guten Ergebnis führen. Insofern sollte man mindestens 10 Stunden bzw. Vielfache von der zum Routen benötigten Zeit einplanen.

Das Design konnte durch iterativen Ansatz auf eine drittel Platine untergebracht werden. Die ersten Ansätze haben sich dafür nicht geeignet.

Funktionsüberprüfung

- Schaltung erzeugt Kurve nur bei 10-1k Hz, tausche 2,2uF Kondensator mit 22nF aus. Funktion bei 0.1 bis 10Hz hergestellt. Der Tastenanschlag kann nun 0.1s bis 10s lang sein.

- Vorwiderstände von Attack und Release sind zu klein, ADSR Kurve verschwindet bei kleinster Potentiometereinstellung. Vorwiderstände werden um zwei Zehnerpotenzen angehoben.

- Ausgangsamplitude der ADSR entspricht mit 8V nicht den Anforderungen der VCA 5V Eingang.

Planungsfehler, Spannungsteiler muss nachträglich integriert werden, um die Amplitude zu verringern. - Eingangsverstärker beeinflusst den Offset des Ausgangs, sofern die Gate-Collectorspannung des Entladetransistors über 5V beträgt. Daher nur verwenden, wenn Verstärkung Eingangsseitig auch gebraucht wird.

- Ausgangsverstärker wird nicht gebraucht, wird daher in einen Spannungsteiler umgebaut.

Aufbau und Wartung der Schaltung

Auf der nachfolgenden Seite befindet sich ein Bild von den Schnittstellen der Schaltung. Zum Abgleich wurden die wichtigen Signale dargestellt.