Inhalt des Dokuments

Tipps für das Platinenlayout

Beim Erstellen eines Platinenlayouts gibt es einige spannende Möglichkeiten, sich in den Fuß zu schießen. Häufig fallen solche Fehler erst beim Bestücken oder Testen der Platine auf. Vor grobem Unfug beim Routen warnt zwar bereits der DRC (so man ihn denn benutzt), allerdings kann man viele Probleme vermeiden, wenn man während des Layoutens einige Kleinigkeiten beachtet.

Spiegeln von Bauteilen in EAGLE

Vorsicht mit Bauteilen, deren Polung nicht beliebig ist (z. B. Elkos und ICs)! Während man im Schematic die Bauteile beliebig drehen und spiegeln kann, bewirkt das Spiegeln mit  "Mirror" im Board, daß das Bauteil von der Platinenoberseite auf die -unterseite verschoben wird. Passiert das versehentlich, sitzen anschließend die Pins an den falschen Stellen. Um schnell herauszufinden, auf welcher Seite der Platine ein Bauteil sitzt, kann man testweise die Ebenen tPlace und bPlace ein- und ausschalten.

"Mirror" im Board, daß das Bauteil von der Platinenoberseite auf die -unterseite verschoben wird. Passiert das versehentlich, sitzen anschließend die Pins an den falschen Stellen. Um schnell herauszufinden, auf welcher Seite der Platine ein Bauteil sitzt, kann man testweise die Ebenen tPlace und bPlace ein- und ausschalten.

EAGLE plaziert die Bauteile beim Erzeugen des Boards auf der Platinenoberseite. In der Regel ist das auch die Seite, auf der Ihr sie haben wollt. Löcher bohren, Bauteilebeinchen von oben durchstecken und an den Leiterbahnen auf der Platinenunterseite festlöten. Wer jedoch SMD benutzt, packt Bauteil und Leiterbahn auf die gleiche Seite.

Lötmöglichkeiten an Bauteilen

Bauteile wie beispielsweise bedrahtete Widerstände und LEDs lassen sich relativ einfach von der Oberseite festlöten und eignen sich deshalb unter anderem gut als Übergangsstelle zwischen Top- und Bottom-Layer. Stecker hingegen sitzen üblicherweise mit dem Gehäuse direkt auf der Platine und können deshalb nur von unten angelötet werden! IC-Sockel und Stiftleisten bilden ein Zwischending: Je nach Bauart (und Geschick beim Löten) lassen sie sich auch von oben anlöten.

Werft also vor dem Routen einen Blick in die Kataloge, um herauszufinden, wie die Bauteile "im wirklichen Leben" aussehen und ob es sie ggf. auch in anderen Bauformen gibt.

Platinenbeschriftung

Allein durch scharfes Hinkucken sieht man einer Platine häufig nicht an, wozu sie eigentlich gedacht ist. Beschriftungen sind hier eine große Hilfe!

- Für welchen Teil des Geräts ist die Platine zuständig?

- Welches Projekt überhaupt?

- Wer ist schuld?

- Wann wurde die Platine erstellt (evtl. Versionsnummern, falls es mehrere Versionen gibt)?

- Wo wird welches Signal mit welcher Polung angeschlossen?

- Welche ist die Oberseite (Top-Layer) der Platine, welche die Unterseite (Bottom-Layer)?

- …

Meßpunkte

Für Fehlersuche und das Durchmessen der Schaltung sind vorher eingeplante Meßpunkte sehr hilfreich. Gliedert sich z. B. die Schaltung in mehrere Funktionsblöcke, sollten Ein- und Ausgänge dieser Blöcke gut mit den Meßspitzen eines Multimeters oder Oszilloskops erreichbar sein. Für die Meßpunkte kann man in EAGLE unter anderem Bauteile aus den Bibliotheken solpad und pinhead verwenden. Auch die Beschriftung dieser Meßpunkte auf der Platine spart viel Zeit beim Durchmessen.

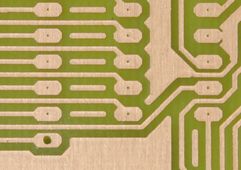

Abstand und Größe der Leiterbahnen/Pads

Um Kurzschlüsse zu vermeiden, muß zwischen Leiterbahnen und Pads ausreichend Platz gelassen werden. Falls Leiterbahnen z. B. zwischen IC-Beinen verlegt werden, kann man die Leiterbahndicke auf diesem Abschnitt reduzieren. Übertreiben sollte man es hier allerdings nicht, da sehr dünne Leiterbahnen beim Ätzen schneller kaputt gehen können.

Höhere Ströme und Spannungen setzen natürlich auch dickere Leiterbahnen und größeres Isolate voraus. In den Laboren liegen kleine Kärtchen (angekettet an die Tische), auf denen unter anderem Angaben zu diesem Thema zu finden sind. In der Regel benutzen wir im Projektlabor Platinen mit einer 35 μm dicken Kupferbeschichtung.

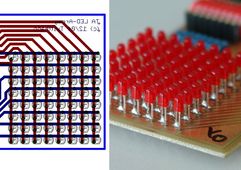

Winzige Vias

- Hier fällt das Löten nachher schon schwer – aufgebohrte Durchkontaktierung (0,8 mm)

- © Projektlabor TUB

EAGLE setzt beim Wechseln der Platinenseite (Top ↔ Bottom) während des Routens sogenannte Vias. In der industriellen Fertigung entstehen dort später von innen metallisierte Löcher, über die beide Seiten miteinander verbunden sind. Für Eure eigenen Platinen könnt Ihr hier zu einem kurzen Stück Draht (oder noch besser: ein Hohlniet) greifen, den Ihr auf beiden Seiten anlötet.

Ist nun der Durchmesser der Kupferfläche um das Via herum zu klein gewählt, gibt es nach dem Bohren der Löcher an diesen Stellen nicht mehr genug Kupferfläche zum einfachen Anlöten. Die Vias sollten deshalb groß genug gewählt werden. Einen guten Anhaltspunkt bieten meist die Pads der anderen Bauteile.

Drill Aid

Um später beim Bohren der Platinen besser die Mitte der Pads zu treffen, sollte man vor dem Ausdrucken des Layouts die Bohrlöcher im Board verkleinern. Das ULP-Skript drill-aid.ulp nimmt einem diese Arbeit ab.

Die Voreinstellung von 0,3 mm für den Durchmesser kann unverändert beibehalten werden. Wer auch mit größeren Zentrierlöchern noch gut zurecht kommt, kann den Durchmesser gerne etwas vergrößern und damit im Endeffekt die Bohrer schonen. Die müssen dann weniger Kupfer bohren und werden nicht so schnell stumpf.

Platz für Busstecker und Frontplatte

Die Elektronik der meisten Geräte, die im Projektlabor entstehen, landet als Einschub hochkant in einem 19-Zoll-Gehäuse. Jeder dieser Einschübe besteht aus einer Platine im Europakartenformat (160×100 mm) mit einem 64-poligen Busstecker am hinteren Ende und einer Frontplatte auf der gegenüberliegenden Seite. Weil sowohl dieser Stecker als auch Frontplattenbefestigung und Führungsschienen für die Einschübe etwas Platz benötigen, steht Euch nicht die gesamte Platine für das Layout zur Verfügung.

Fügt also, bevor Ihr mit dem Layout beginnt, im Schematic den Busstecker ein (zu finden unter 19inch » VG64 » VG64P) und verbindet die entsprechenden Pins mit dem Rest Eurer Schaltung. Im Board bekommt Ihr somit neben den Platinenumrissen und Seitenrändern praktischerweise auch gleich noch Bohrlöcher für die Frontplatten Eurer Einschübe.

Vias in Masseflächen

Das Durchkontaktieren des Massesignals auf die andere Platinenseite kann man ganz normal mit einem Via bewerkstelligen. Beim Erstellen der Massefläche nach dem Routen gibt es jedoch ein kleines Problem: die Massevias sitzen mitten in einer großen Massefläche aus Kupfer, und beim Löten fließt deshalb die Wärme an dieser Stelle sehr schnell ab. Ohne ausreichend Wärme keine vernünftige Lötstelle. Also was tun?

Für normale Pins kann man über die Option "Thermals" des Massepolygons automatisch Thermalstege einfügen lassen, die dieses Abfließen verhindern. Für die beschriebenen Massevias geht dies ebenfalls automatisch, allerdings ist die entsprechende Option etwas versteckt: Man öffnet mit einem Klick auf  "DRC" den Design Rule Check und aktiviert im Kärtchen Supply die Option "Generate thermals for via". Die Vias erhalten nun automatisch Thermalstege, während das Massepolygon selber einen kleinen Abstand um die Vias herum einhält.

"DRC" den Design Rule Check und aktiviert im Kärtchen Supply die Option "Generate thermals for via". Die Vias erhalten nun automatisch Thermalstege, während das Massepolygon selber einen kleinen Abstand um die Vias herum einhält.